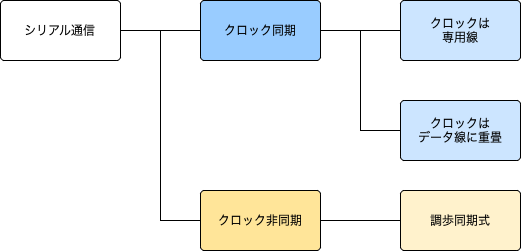

異なるデバイス(機器)間を接続するシリアル通信は、『クロック同期式』と『クロック非同期式』に大別できます。

更に、『クロック同期式』は、クロックをデータ線と別線で伝達する方式と、クロックをデータ線に重畳して(重ねて)伝達する方式があります。

本記事では、これらシリアル通信の仕組みや違いについて、簡潔に、分かりやすく解説します。

✔️【シリアル通信】クロック同期式と非同期式の違い

✔️クロック同期式シリアル通信の動作原理

✔️非同期式シリアル通信の動作原理

✔️各通信方式が適用されている通信規格

クロック同期式と非同期式の違い

デバイス(機器)間を接続するシリアル通信方式には、『クロック同期式』と『クロック非同期式』(=『調歩同期式』)があります。

以下、これらの違いについて簡単に説明します。

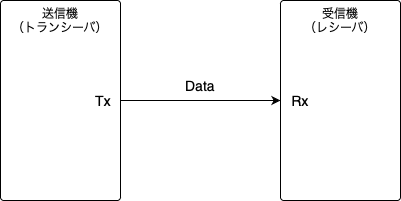

通信は、トランスミッタ(送信機)とレシーバ(受信機)で構成されます。

また、送信データや、データを送信するポートをTx(またはTxD)、受信データや、受信するポートをRx(RxD)と表記します。

トランスミッタとレシーバは、あるクロックを基準に、データの送受信タイミングを決めます。

このクロックにおいて、

トランスミッタとレシーバが、

同一のクロックを使用する方式を『クロック同期式』

別々のクロックを使用する(タイミングを見きわめて通信する)方式を『非同期式(以下調歩同期式)』

といいます。

クロック同期式

トランスミッタは、送信タイミングの基準となるクロックを、データと一緒にレシーバへ供給します。

レシーバは、そのクロックを基準にデータを取り込みます。

調歩同期式

トランスミッタは、あらかじめ設定されたルールに従い、自身のクロックを基準にデータのみをレシーバへ供給します

レシーバも、あらかじめ設定されたルールに従い、自身のクロックを基準にデータを取り込みます。

以下、クロック同期式と調歩同期式の特徴について、詳しく解説していきます。

クロック同期式シリアル通信の特徴

クロック同期式シリアル通信は、クロックをデータ線と別線(クロック専用線)で伝達する方式と、クロックをデータ線に重畳して(重ねて)伝達する方式(エンベデッド・クロック方式)があります。

クロック同期式(クロックを専用線で伝達)

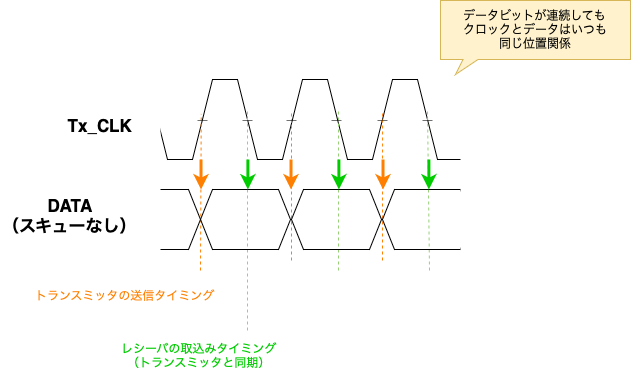

クロック同期式のシリアル通信は、トランスミッタとレシーバが同一クロックを基準に動作することで、データの送受信タイミングを一意に特定でき、両者で送受信タイミングの認識がズレません。

例えば、トランスミッタがクロックの立ち上がりエッジでデータを送信し、レシーバが、同じクロックの次の立ち下がりエッジでデータを受信する、といったように、データを1ビットずつ、確実に送受信できます。

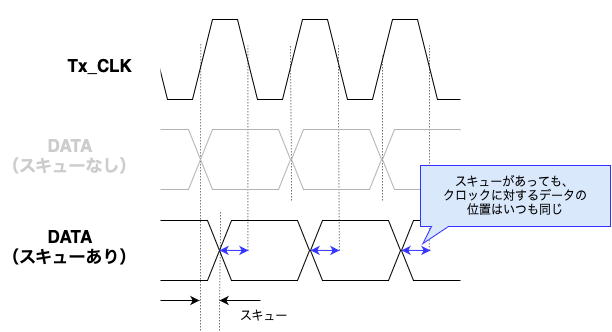

クロックとデータが別線の場合、配線長差によるスキューが発生しますが、これはデータビット毎に蓄積されるものではなく、後述する調歩同期式の問題(1ビットごとに蓄積するタイミングのズレ)とは別ものです。

同期クロックによって、トランスミッタは正しい送信タイミングを、レシーバは正しい受信タイミングを、それぞれ認識することができます。

クロック同期式は、たくさんのビット列を連続して送受信できるため、転送レートを上げやすいという特徴があります。

一方、データと一緒にクロックを送信する分、回路やケーブルが煩雑になります(高コスト)。

また、クロック線とデータ線の配線長差によるスキューを考慮する必要があります。

クロック同期式(クロック線)を採用した通信方式としては、SPI(Serial Peripheral Interface)や、I2Cがあります。

クロック同期式(エンベデッド・クロック方式)

同期用のクロックを専用線ではなく、データ線に重畳して(埋め込んで)伝送する同期式シリアル通信をエンベデッド・クロック方式といいます。

クロック同期式の論理的な考え方は、上記クロック専用線方式と同じです。

エンベデッド・クロック方式は、データ列を「0」または「1」が一定以上連続しないデータ列(シンボル)に変換し、一定時間毎に必ずデータの変化が起こるようにします。

シンボルの内容に意味は無く、変換用の計算式もありません。

「このデータ列」は「このシンボル」、

という具合に変換テーブルが決められています。

シンボルは一定時間毎に必ずデータの変化が起こる並びしか使用できないため、変換前のデータ列よりも多くのデータ長を必要とします。

レシーバは、データの変化点を検出し、PLLを用いて自身の取り込みクロックと同期することで、トランスミッタ側のクロックを再現できます(クロック・リカバリ)。

変換前のデータ列をシンボルに変換する手法としては8b10b(エイト・ビー・テン・ビー)方式が代表的です。

8b10b方式は、8ビットのデータを、HighまたはLowが4ビット以上連続しない10ビットのシンボルに変換します。

8b10b方式は、2ビット分の伝送帯域をロスする代わりに、クロック専用線が不要で、配線スキューを考慮する必要がありません。

配線スキューの考慮が不要であるということは、シリアル通信の高速化を考える上で非常に大きな強みとなります。

エンベデッド・クロック方式を採用した通信方式としては、USBやPCI exressが代表的です。

エンベデッド・クロック方式は上記利点とは別の観点でACカップリングを用いた転送方式には必須の技術という側面がありますが、本記事の内容から脱線するため割愛します。

調歩同期式シリアル通信の特徴

調歩同期式シリアル通信は、トランスミッタとレシーバのタイミングを同期できないため、両者はあらかじめ設定されたプロトコル(ルール)に従い、タイミングを見計らって通信します。

すごく簡単に言うと、下記のイメージです。

トランスミッタ:「設定に従うと、このタイミングでデータを送ればレシーバが受信できるはず」

レシーバ :「設定に従うと、このタイミングであれば有効データを取り込めるはず」

このように、トランスミッタとレシーバは、データの正確な送受信タイミングを認識(特定)することができません。

調歩同期式は、通信開始を意味するスタートビットを基準に、それに続く連続したデータを、互いのタイミングで送受信していきます。

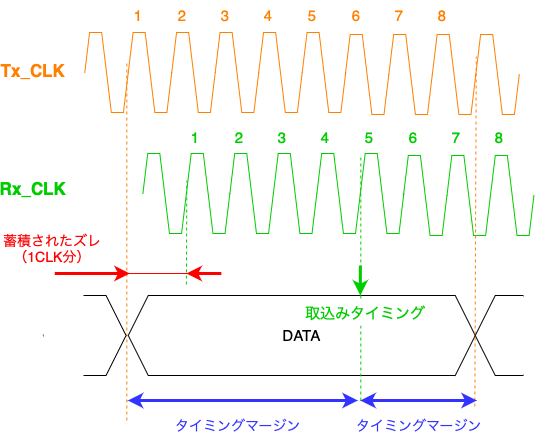

ここで、両者のクロックは非同期ですので、周期、位相に「ズレ」が生じます。

この「ズレ」は、データを1ビット送受信するごとに蓄積され大きくなり、やがては正しいデータを取込めなくなります(下図)。

このため、調歩同期式では、一度に連続して通信できるデータビットの数が制限されます。

また、トランスミッタとレシーバのクロックは、周波数が完全に一致していたとしても非同期であるが故に、最大1周期分の位相差が発生します。

よって、1ビットのデータを取り込むために、複数クロックが必要となります。

なお、データ1ビットを送受信するために要するクロックの数が多いほど、レシーバでの取り込みタイミングのマージンが増え、データ長(連続して通信できるビット数)を増やすことができます。

例えば、8クロックで1ビットを通信する場合を考えます。

トランスミッタは1クロック目の立ち上がりエッジでデータを送信するものとします。

すると、レシーバは5クロック目の立ち上がりエッジでデータを取込めば、データ幅のちょうど真ん中を狙うことができる、といった具合です。

ただし、トランスミッタのクロックとレシーバのクロックは非同期ですので、実際にレシーバが取り込むタイミングは、データのちょうど真ん中にはなりません。

この例では、(Tx_CLKとRx_CLKのズレが蓄積されることにより、)データを取り込む際のホールドマージンが減少しています。

次に、例えば16クロックで1ビットを通信する場合を考えます。

トランスミッタは1クロック目の立ち上がりエッジでデータを送信し、レシーバは9クロック目の立ち上がりエッジでデータを取り込むこととします。

上記8ビットの例よりも、データ幅に対する1クロック分のズレの影響が小さくなり、タイミングマージンが大きくとれます。

これにより、データ長を長くできます。

非同期式は転送レートを上げにくい一方、クロック線が不要な分、回路やケーブルが単純(低コスト)になります。

調歩同期式を採用した通信方式としては、RS232Cや、UARTがあります。

※UARTは厳密には通信「規格」ではありません。

UARTについては下記の記事で詳しく解説しています!

コメント