LVDS(Low Voltage Differential Signal)は差動データ伝送の最も一般的な規格です。

ディスプレイ・モニタの描画データ伝送や、コピー機の画像データ伝送など、様々なアプリケーションに採用されています。本記事では、LVDSの基本、動作原理、規格内容について分かりやすく解説します。

✔️LVDSの特徴とメリット

✔️LVDSの動作原理

✔️LVDS規格の内容

LVDSとは何か

LVDSはTIA/EIA(米国電気通信工業会/米国電子工業会)によって標準化された差動データ伝送の規格で、約350mVの低振幅信号で高速シリアル伝送を行うインターフェースです。

本規格は、電気的特性(ドライバとレシーバの入出力特性)のみを規定します。

通信プロトコルやケーブル特性をあえて規定しないことで、通信全体を規定する他の規格の物理層として参照されることを意図した規格です。

LVDSは、CMOSやTTLなどシングルエンドの伝送方式と比較すると、低消費電力、高いノイズ耐性、高いデータレートが実現可能、といった特徴があります。

以下、LVDSの動作原理と共に、これらの特徴について解説します。

LVDSの動作原理

上述したように、LVDSは物理層のみを規定した規格です。

以下、LVDSのハードウエアについて説明します。

ハードウエアの構成

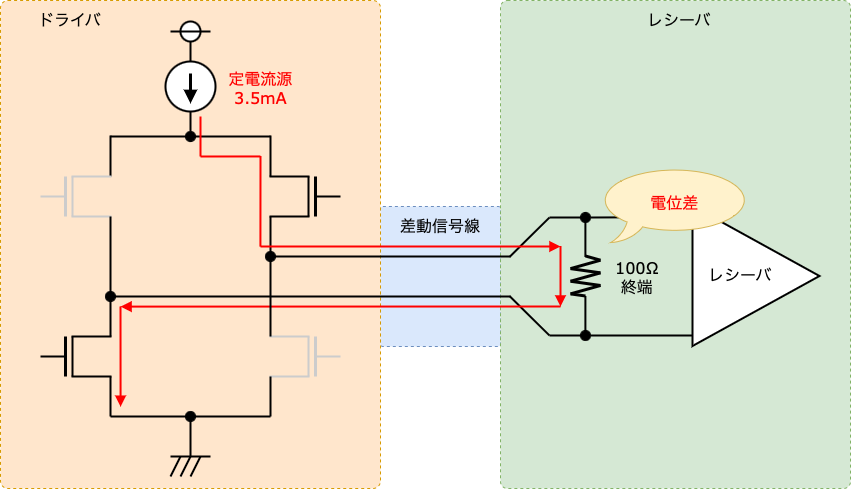

LVDSは、ドライバ、レシーバおよび、双方をつなぐ差動信号線から構成されます。

(差動信号線とは何か?が分からなくても、以下の記事を読めば理解できます)

ドライバには、3.5mAの電流を流す定電流源(これはデバイスの電源電圧に依存しません)があり、レシーバ側にある100Ωの終端抵抗に電流が流れます(下図)。

※この電流の向きを、本記事では「+方向」とします。

ドライバは、回路を切り替えて電流の向きを逆方向(-方向)にすることもでき、レシーバは終端抵抗の両端に発生する電位差の±を検出します。

差動伝送の原理

上記LVDS構成では、ドライバが流す定電流3.5mAと終端抵抗100Ωは固定値ですので、レシーバで検出する電位差も固定値となります。

これはオームの法則より、3.5mA*100Ω=350mVとなります。

見慣れたシングルエンド信号はGND基準の電圧レベルで二値を表現しますが、差動信号は電流を流す向きを制御することで、Hレベル/Lレベルを表現します。

以下に詳しく解説していきます。

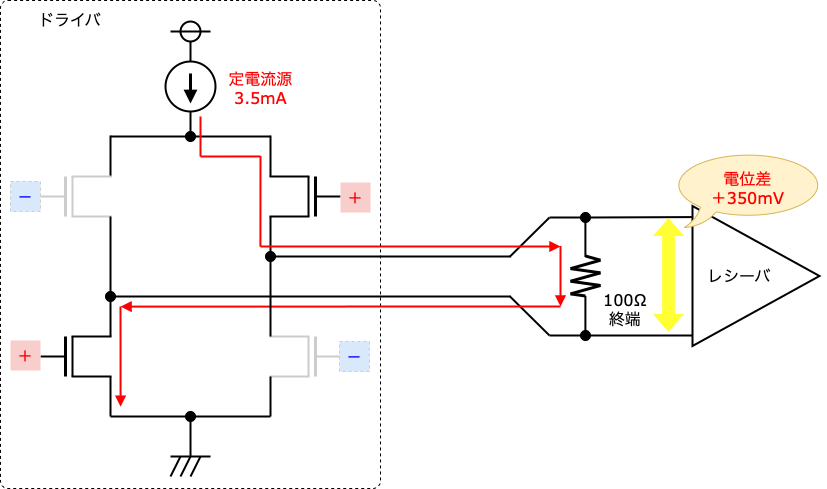

+方向に電流を流す場合

+方向に電流が流れるとき、オームの法則により、レシーバの終端抵抗間には、

+3.5mA * 100Ω = +350mV の電位差が生じます。

差動信号の極性が「+」の場合、レシーバは信号の状態をHレベルと認識します。

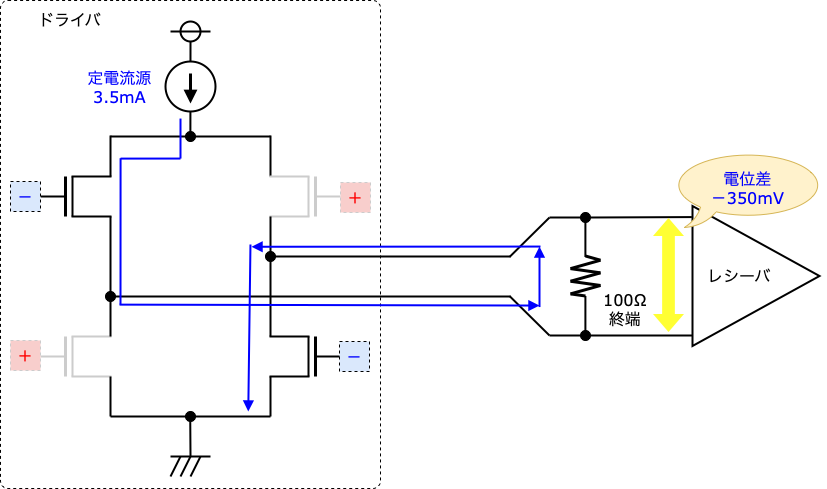

ー方向に電流を流す場合

-(マイナス)方向に電流が流れるとき、オームの法則により、レシーバの終端抵抗には、

-3.5mA*100Ω = -350mV の電位差が生じます。

差動信号の極性が「-」の場合、レシーバは信号の状態をLレベルと認識します。

差動伝送方式とシングルエンド伝送方式

以上のように、終端抵抗両端の電位差がプラスかマイナスかの二値で信号伝達する方式を「差動伝送方式(ディファレンシャル方式)」といい、LVDSの場合は一般に±350mVの振幅で駆動します。

シングルエンド伝送方式

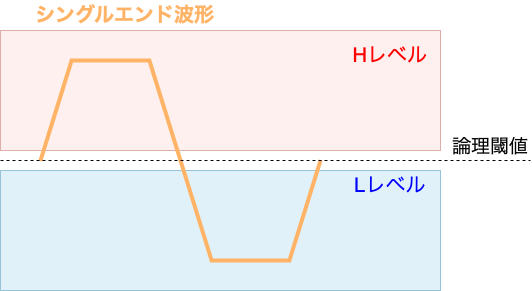

なお、GND電位に対する電位の大小でHレベルとLレベルを判別する方式を、「シングルエンド伝送方式」といいます。

CMOSやTTLに代表される、IO規格はシングルエンド方式です。

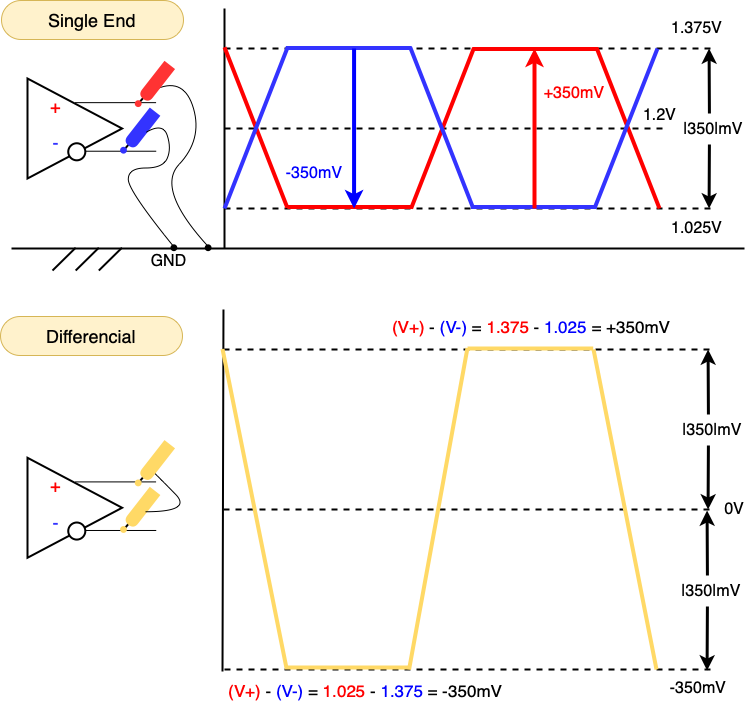

LVDSのシングルエンド波形と差動波形

LVDSの、シングルエンド波形(プラス、マイナスそれぞれをGND電位に対して測定)と差動波形を下図に示します。

LVDSのシングルエンド波形は1.2Vのオフセット電圧を基準に350mVの振幅を持ちます。

差動波形において差動電位は、

【シングルエンドの+電位】-【シングルエンドのマイナス電位】

で計算できますので、0Vを基準に、±350mVの振幅を持つことがわかります。

LVDS(差動伝送方式)のメリット

差動伝送方式の動作原理は説明しましたが、差動伝送することどのようなメリットがあるのでしょうか?

本記事の冒頭でも触れましたが、LVDSには下記のメリットがあります。

✔️高いデータレート

✔️低消費電力

✔️低コスト

以下、これらの特徴について説明していきます。

ノイズに強い

差動信号はプラス側とマイナス側の電位「差」で信号を伝送するため、2本の信号線に等しく発生するコモンモードノイズの影響を受けません。(下図)

このように、差動線で発生したコモンモードノイズはレシーバで除去されます。

また、差動伝送方式は以下の特徴を持つため、放射するノイズも低減します。

✔️回路が常時オン(Hレベル、Lレベルいずれも向きの異なる電流が流れる)ため、

トランジスタのターンオン/オフ時のスイッチングノイズが発生しない

高いデータレート

信号を高速に伝達するためには、信号の遷移時間(立ち上がり/立ち下がり時間)が課題になります。

周波数が高い信号の遷移時間が長いと振幅を保てない(レベルが減衰する)ためです。

信号の遷移時間を短くするためには、信号の振幅を低くすることが有効です。

振幅が低いと論理閾値に対するノイズマージンを確保しにくくなりますが、差動伝送方式はノイズが問題になりにくい性質があるため、この部分をカバーできる(振幅を下げやすい)というメリットがあります。

LVDSの実使用条件における推奨最大データレートは655Mbpsです(理論上の無損失伝送路における最大値は1.923Gbpsにもなります)。

低消費電力

LVDSレシーバの入力インピーダンスは非常に高いため、回路に流れる電流のほとんどが100Ωの終端抵抗を流れます。

終端抵抗で消費される電力は、3.5mA*350mV = 1.2mW となります。

これは、シングルエンド伝送方式のCMOSやTTLと比較して1/10以下の消費電力です。

低コスト

上述したように、ドライバ、レシーバおよび、終端抵抗のみの簡易な構成で上記メリットを享受できます。

LVDS規格の内容(電気的特性)

LVDS規格はドライバとレシーバの電気的特性のみを規定します。

LVDSデバイスを製造するメーカは、仕様の上下限でも本仕様を逸脱しないようデバイスを設計するため、実際のデータシートにはより厳しい値が規定されているはずです。

本規格は、LVDSを謳うドライバやレシーバが、最低限守らなければならない約束事と言い換えることもできます。

以下、規格で定義される具体的な電気特性について詳しく解説します。

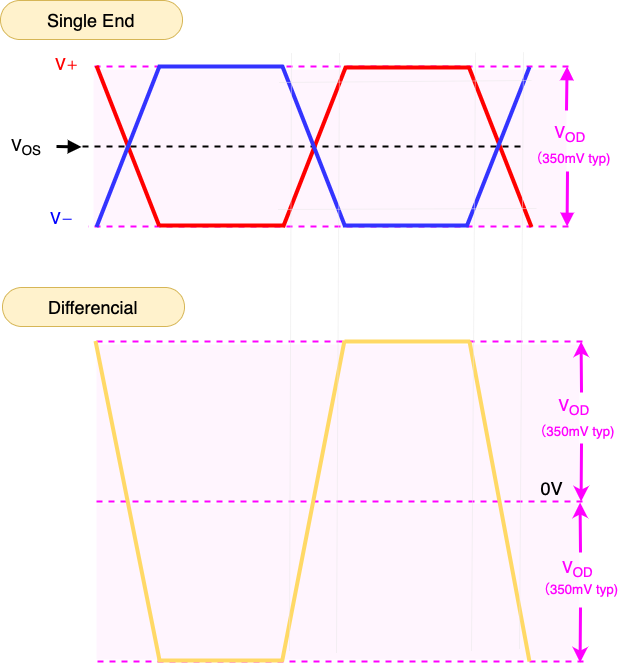

差動出力電圧(VOD)

差動出力電圧 VODとは、信号の振幅、つまり上述の±「350mV」のことです。

LVDSをシングルエンド信号として観た場合、

ドライバの出力電圧は、プラス、マイナスともに、VODの振幅を持つ必要があります。

※振幅中央の電圧はオフセット電圧(VOS)として規定されます(後述)。

差動信号において、VODは±に振れますが、規格で定義されるVODは絶対値「|VOD|」を意味します。

これを差動信号として観ると、0Vを基準にした±VODの振幅をもった信号となります。

VODの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| VOD | 247mV | 454mV |

シングルエンドV+が「H」、V-が「L」のときの差動電圧

上図に示したように、シングルエンドでV+、V-を見た場合、

V+=VOS+VOD/2、V-=VOS-VOD/2 となります。

ここで、差動電圧を計算してみます。

差動電圧 =(V+)-( V-)= (VOS+VOD/2)-(VOS-VOD/2)= +VOD

よって、極性が+、振幅がVOD(=350mV)の差動電圧であることが分かります。

当然といえば当然ですが..。

シングルエンドV+が「L」、V-が「H」のときの差動電圧

上記シングルエンドV+が「H」、V-が「L」のときと同様に、

差動電圧 =(V+)-( V-)= (VOS-VOD/2)-(VOS+VOD/2)= -VOD

よって、極性がー、振幅がVOD(=350mV)の差動電圧であることが分かります。

オフセット電圧(VOS)

オフセット電圧(VOS)は、シングルエンドで定義される電圧で、その名の通り、ドライバ出力のオフセット電圧です。

+側、-側の出力電圧はVOSを中心にVODの振幅を持ちます。

VOSの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| VOS | 1.125V | 1.375V |

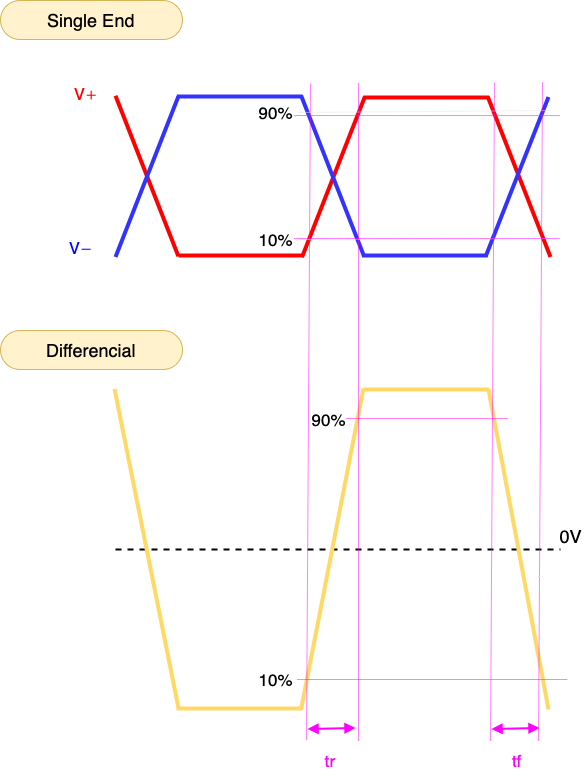

出力立ち上がり/立ち下がり電圧(tr/tf)

ドライバが出力する信号には立ち上がり/立ち下がり時間(tr/tf)が規定されています。

tr/tfの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| tr/tf (200Mbps以上) | 0.26ns | 1.5ns |

| tr/tf (200Mbps未満) | 0.26ns | bit幅の30% |

短絡電流(IS)

LVDSの出力端子がGNDと短絡した際に流れることを許容される最大電流が規定されています。

これはドライバに対する規定となります。

ISの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| IS | - | |24mA| |

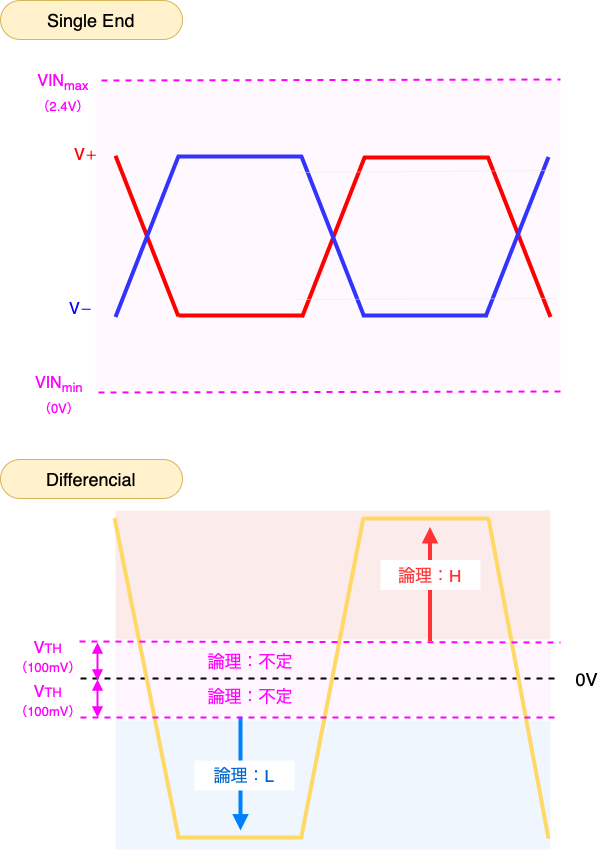

入力電圧範囲(VI)、入力閾値電圧(VTH)

レシーバに要求される仕様として、入力電圧範囲(VI)、入力電圧閾値(VTH)があります。

レシーバは、(少なくとも)入力電圧範囲(VI)で規定される入力電圧を許容する必要があります。

入力電圧範囲(VI)はシングルエンドの電圧値として規定されます。

また、レシーバは、差動信号の2値を判定するための閾値を持ちますが、これは|入力電圧閾値(VTH)|として規定されます。

入力閾値電圧(VTH)は差動電圧値として規定されます。

入力電圧閾値は絶対値表記なので少し分かりにくいのですが、例えばHレベル時、ドライバは+VTH以上をドライブすることが要求され、レシーバはHレベル判定閾値が0V 〜 +VTHであることを要求されます。

VI、VTHの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| VI | 0V | 2.4V |

| VTH | - | 100mV |

レシーバに対する入力電圧として、シングルエンド信号に対してはレシーバが破損に至らないよう最大(最小)電圧を、差動信号に対しては信号の論理判定閾値を規定しているということになります。

入力電流(IIN)

LVDSは定電流回路で構成されるため、レシーバの入力端子(V+、V-)に流れ込む電流が大きかったり、バラツキが大きいと、100Ωの終端抵抗にて所望の差動電圧が得られなくなってしまいます。

このため、入力電流の最大値が規定されています。

IINの仕様値

| 項目 | 最小 | 最大 |

|---|---|---|

| IIN | - | |20uA| |

LVDSの応用例

LVDSの応用例として、LVDSレシーバICや、LVDS SerDesがあります。

これらのデバイスについては、下記の記事で詳しく説明しています!

コメント