クロック同期型のLVDSデータをCMOSやTTL等シングルエンドのパラレルデータに変換するLVDSデシリアライザおよび、その逆を行うLVDSシリアライザがあります。

これらは合わせてLVDS SerDes(Seriarizer/Deseriarizer)と言います(サーデスと読みます)。

LVDS SerDesは、FPGAに内蔵されているケースもありますが、本記事では専用のデシリアライザICを例に、その動作原理やデバイスのデータシートに規定されるパラメータについて解説します。

特に、重要なパラメータである「スイッチング特性」はその意味を理解しにくいですが、SerDesを用いた回路設計を行う上で欠かせないポイントとなるため、詳しく解説します。

本記事の内容は、LVDSに関する基本的な知識が前提となります。

LVDSの基本については下記に詳しくまとめてありますので、合わせて参照下さい!

✔️LVDS SerDesの動作原理(Desを例に解説)

✔️デシリアライザICのスイッチング特性(データシートの読みかた)

LVDS SerDesの動作原理

SerDesはLVDSの特性を活かすことで、高速、低コスト、ノイズ耐性に優れたデータ伝送が可能であるため、ケーブル等で接続された基板間のインターフェース(ディスプレイ・データの伝送等)に用いられます。

LVDS SerDesとはなにか

クロック同期型のLVDSデータをCMOSやTTL等シングルエンドのパラレルデータに変換するLVDSデシリアライザおよび、その逆を行うLVDSシリアライザがあり、これらを合わせてLVDS SerDes(Seriarizer/Deseriarizer)と言います。

以下、デシリアライザを例に、動作原理を解説します。

7:1伝送方式

LVDSデシリアライザは、LVDSクロックに同期したLVDSデータをCMOSやTTL等シングルエンド規格のパラレル信号に変換する回路です。

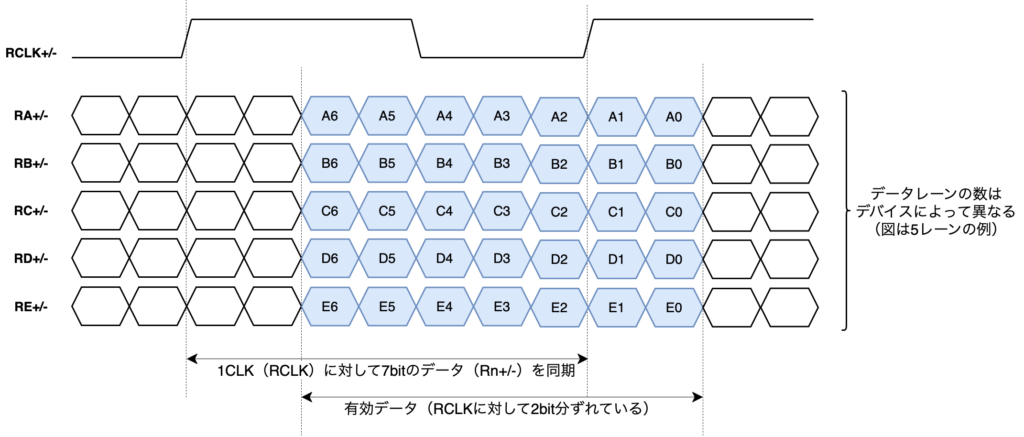

伝送方法はデータ7ビットに対して1クロックで同期をとる方式が主流です(データ6ビットに対して1クロックなど、その他のフォーマットも存在します。これらは7:1方式、6:1方式等と表記されます。以下、7:1方式で説明を行います)。

このクロックをRCLK(Reciever Clock)と表記します。

LVDS SerDes 7:1の仕様では、RCLKはその有効データに対して2ビットずれた位相となります。

7:1方式のタイミングチャートを下図に示します。

RCLK・データ間スキュー

データレーンの数はデバイスによって異なりますが、複数のデータレーンに対して1つのRCLKで同期をとるため、データレーンの数が多いほど、配線スキューへの考慮(ボード上の配線)が難しくなります。

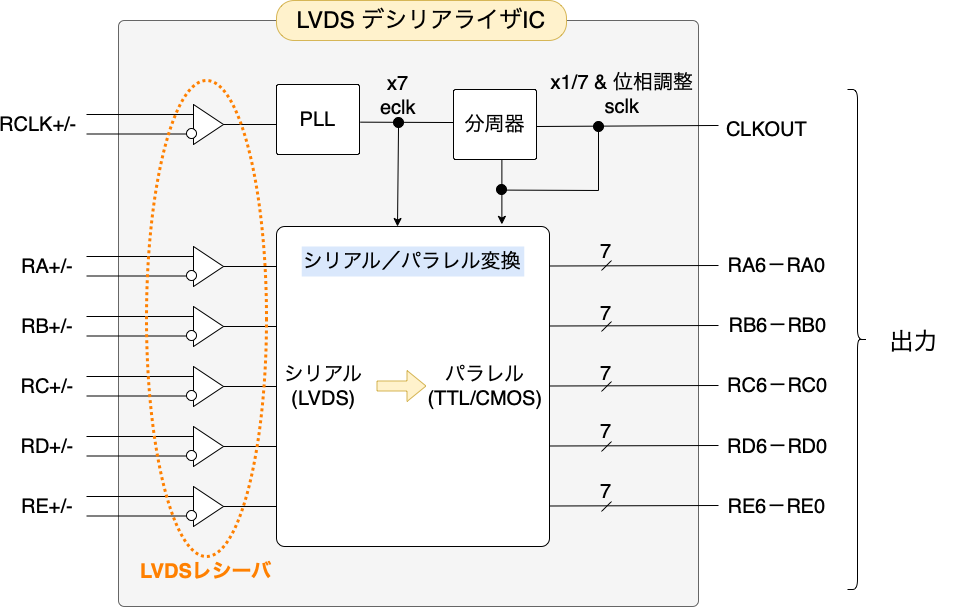

RCLKとデータは、デシリアライザ内のLVDSレシーバへ入力され、シングルエンド信号に変換されますが、このとき、クロックとデータ間にスキューが生じます。

このスキューによりデータ取り込みタイミングのマージンが減少することから、デシリアライザICの入力タイミングは、このレシーバ・スキューを考慮した値としてデータシート上で規定されます。これは、tSK(Receiver Skew Margine)として後述します。

LVDSレシーバの動作原理、スキューの考え方については下記の記事で詳しく解説しています!

デシリアライザの内部動作

ここからはデシリアライザ内部の動作原理となります。

7逓倍クロックと位相シフトクロック

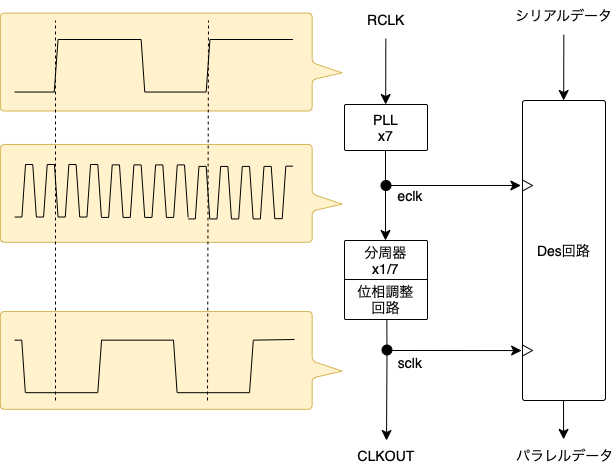

デシリアライザICにはPLLが内蔵されており、RCLKを元に下記2種類のクロックを生成します。

・データ取り込み用の7逓倍クロック(以下、eclkと表記します)

・出力同期用の位相シフトクロック(以下、sclkと表記します)

※eclkとsclkはデシリアライザ内部で完結するクロックですので、専用ICをただ使用するだけであれば気にする必要はありません(ICのデータシートには出てきません)。ここでは、動作原理を説明するために記載しています。

データの取り込みと同期

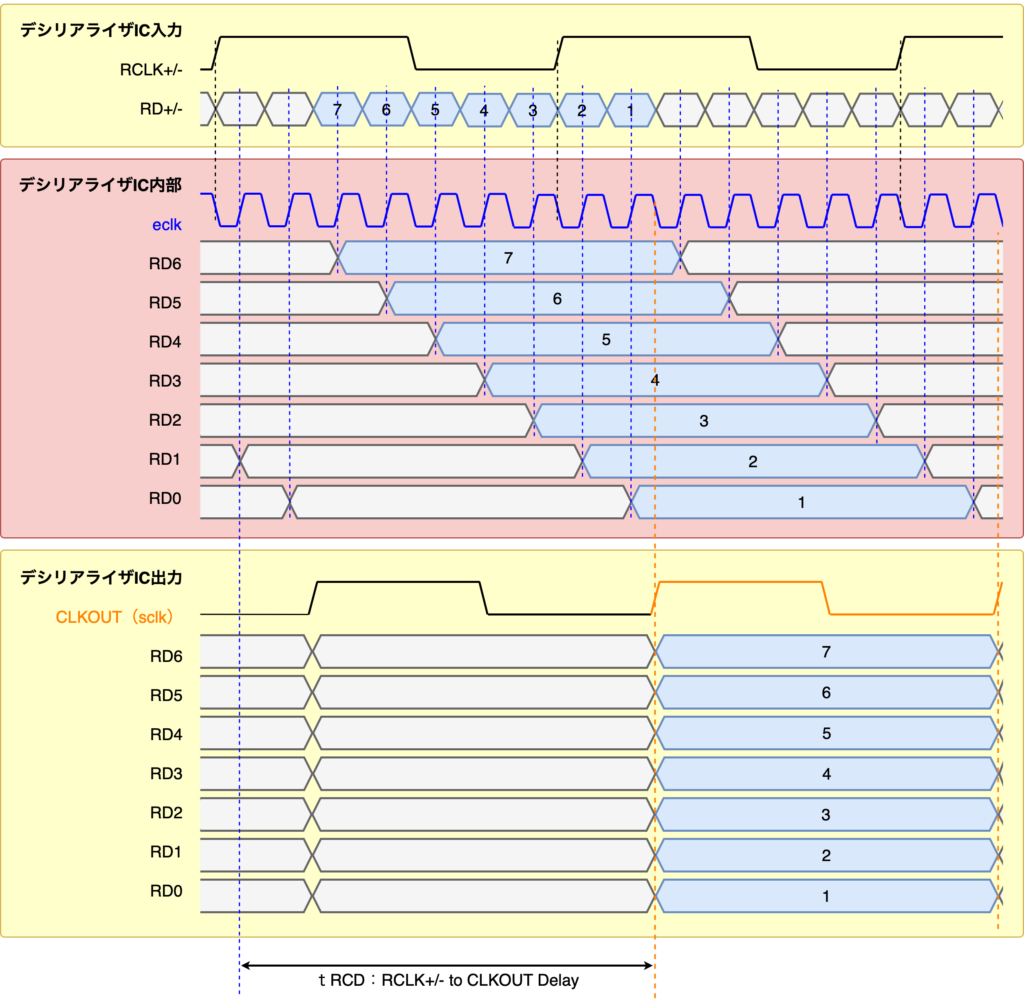

eclkのエッジで取り込まれたシリアルデータは、パラレルデータに変換され、sclkに同期して出力されます。前述したように、RCLKは有効データに対して2ビットのずれがありますが、位相シフトされたsclkを用いることで、出力データは出力クロック(CLKOUT)に同期して出力されます。

なお、RCLKが入力されてからCLKOUTが出力されるまでには、eclkによるデータ取り込み回路やsclkへの同期回路による出力遅延があり、遅延時間が規定されています(tRCD:RCLK+/- to CLKOUT Delayとして後述します)。

タイミングチャート

以上のタイミングチャートを下図に示します。

デシリアライザIC スイッチング特性

ここからは、デシリアライザICのデータシートに実際に記載される電気的特性(特にスイッチング特性)について重要なものを詳しく解説していきます!

tRCP:CLKOUT Period

CLKOUT(デシリアライザICが出力するパラレルデータ同期クロック)の周期を意味します。CLKOUT周期=RCLK周期ですので、単純に、「入力可能なクロック周波数の逆数(の範囲)」が規定されます。

出力クロックの範囲として規定されているので紛らわしいですが、出力クロックの「精度」を規定したパラメータではありません。

tRCH:CLKOUT High Time/tRCL:CLKOUT Low Time

CLKOUTのHレベル幅、Lレベル幅を意味し、単順にRCLK周期(tRCP)の半分が定義されます。

tRS:TTL Data Setup to CLKOUT/TTL Data Hold from CLKOUT

CLKOUTに対する、出力データ(TTL)のセットアップ/ホールド”保証”時間で、後段(パラレル信号を受けるデバイス)の入力タイミングを設計する際に必要となるパラメータです。有効な出力データが確定してからCLKOUTの立ち下りまでの時間および、CLKOUTの立ち下りから出力データが無効となるまでの時間と定義されます。

CLKOUTと出力データには、デバイス構造由来のスキューがあり、CLKOUTは出力データより遅延時間が大きいことが一般的です。

そのため、通常、tRS > tRH となっています。

当然、クロック周波数が早い(tRCPが短い)ほど、本パラメータも厳しい値になるよう規定されています。

余談ですが、メーカーはレシーバのスキューマージンを考慮し、本パラメータそれぞれを最小値(ワースト)で定義しているため、tRSとtRHを足してもtRCP1周期よりも小さな値となります。

tSK:Receiver Skew Margin

本パラメータは、デシリアライザICのレシーバ回路が許容できる入力クロックとデータ間のスキューを意味します(レシーバの入出力間にはスキューが生じるため、後段回路に対するマージンが規定されています)。

デシリアライザICに入力するクロックとデータは本パラメータ(スキューマージン)の範囲内である必要があります。

入力タイミングについては別途、「tRIPn:Input Data Posision n」が規定されており(後述しますが、こちらの規定はtSKを含んだ値となっています)、タイミング規定としてはこちらの方がメインであるため、本パラメータが記載されていないデバイスもあります。

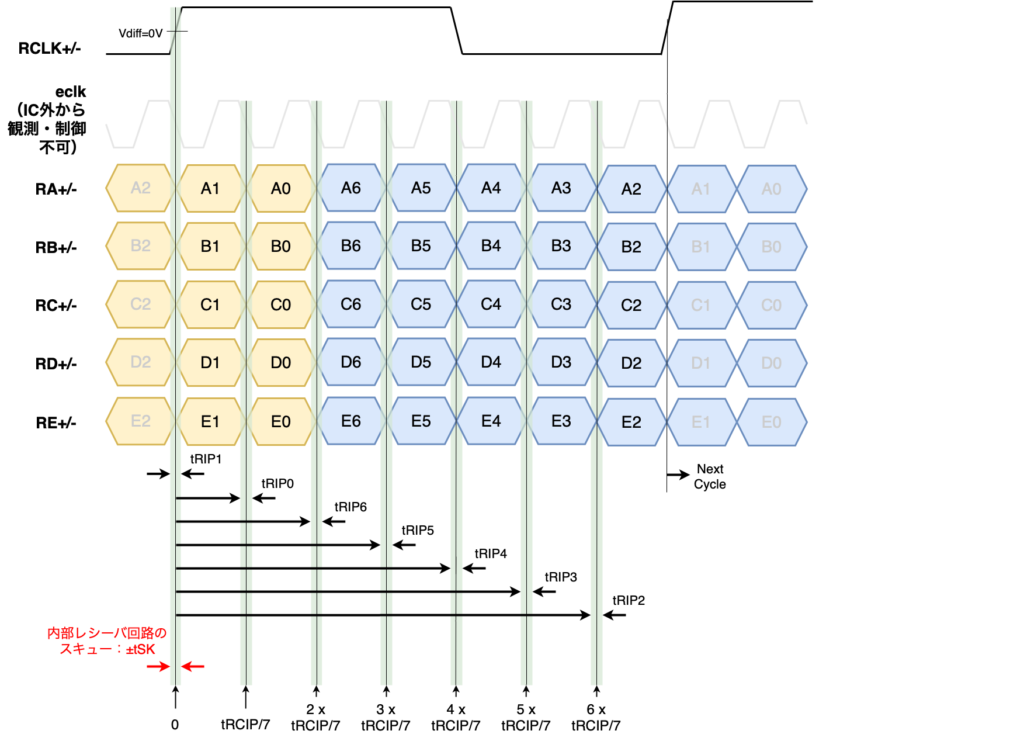

tRIPn:Input Data Position n ※n=0〜6

入力されたシリアルデータは、内蔵PLLでRCLKを7逓倍した高速クロック(eclk)によって取り込まれます。

RCLK基準で観測するデータの取り込みタイミング

よって、eclkの取り込みエッジのタイミングで、各データビットが確定している必要があります(eclkの取り込みエッジとデータビットの変化タイミングが重なってはいけません)。

eclkは、RCLKを元にIC内部で生成されるため、外部から制御・観測することはできませんがRCLKと同期しています。

よって、eclkの取り込みエッジと入力データのタイミングは、RCLKと入力データのタイミングを規定することで間接的に保証されます。

これを規定するのがtRIPです。

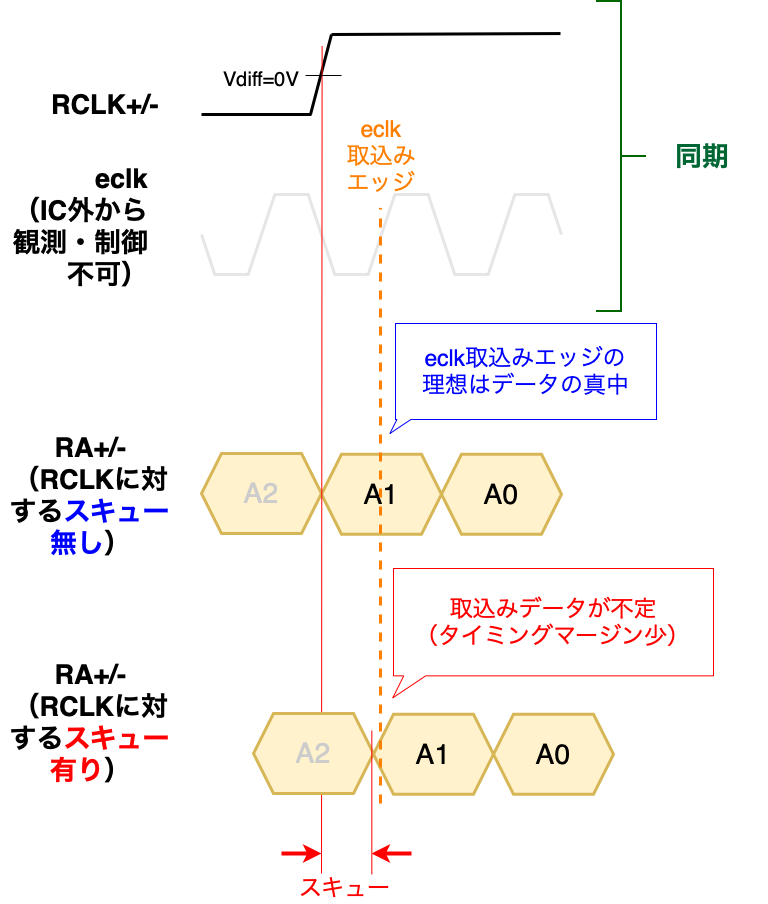

RCLKー入力データ間のスキューが大きいと、これを満足できなくなり、データを正しく取り込めなくなります(下図)。

※LVDSレシーバのスキューの考え方は下記を参照ください。

tRIPはデータビットが変化して良いタイミングを規定

tRIPnは、RCLKのエッジを基準に入力データのタイミング(ポジション)を規定します。tRIPnの「n」にはデータビットの番号(7:1方式では6〜0)が入ります。

すなわち、tRIP6〜tRIP0まで、各データビットのタイミングが定義されます。

少し分かりづらいですが、tRIPnはRCLKの立ち上がりタイミングを基準に、各データビットの変化タイミング(各データビットが変化して良いタイミング)の範囲を規定します。

逆に言えば、各データビットは、tRIP以外のタイミングで有効データを保持する必要があります(eclkの取り込みエッジは、tRIPで規定された範囲外に来ることが保証されます)。

eclkはRCLKと同期していますので、各データビットの取り込みタイミングはRCLK/7bitに内部のスキューマージン(±tSK)を考慮した範囲となります。

例えば、上図では、

tRIP1=±tsk、tRIP0=tRCIP/7、tRIP6=2xtCIP/7、tRIP5=・・・・・・tRIP2=6xtCIP/7

となります。

デバイスによっては(特にFPGA内蔵SerDes回路)、逆に有効データを保持しておく範囲が規定されていることがありますが、考え方は同じです。

コメント