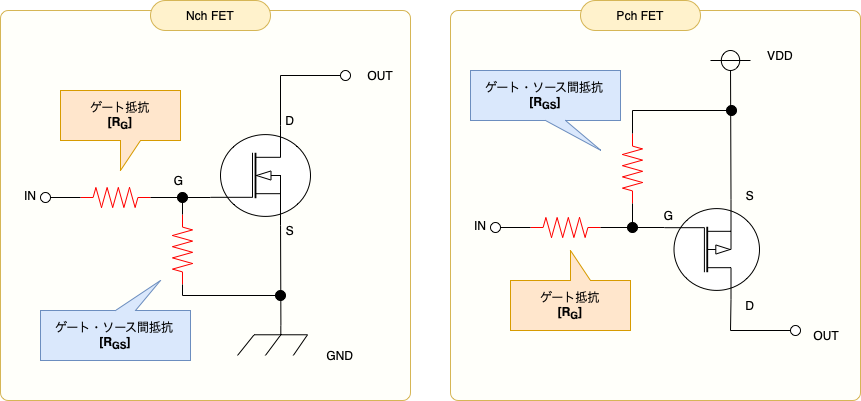

MOS-FET(以下”FET”)を用いた回路には、必ずといって良いほど下図のゲート抵抗とゲート・ソース間抵抗が入っています。

ゲート抵抗とゲート・ソース間抵抗は単純な構成ですが、FETの性能を引き出すためには重要な回路です。

本記事では、ゲート抵抗とゲート・ソース間抵抗が必要な理由から定数の決め方まで、詳しく説明していきます!

✔️FETの駆動回路にゲート抵抗、ゲートソース間抵抗が必要な理由

✔️ゲート抵抗、ゲート・ソース間抵抗の定数の決め方

ゲート抵抗

FETのゲートと、ゲートドライバ(本記事ではFETのゲートを駆動させる前段回路のデバイスをこのように表記します)の出力間に挿入する抵抗を一般に”ゲート抵抗”といいます(下図)。

ゲート抵抗が必要な理由

FETのドライブ回路には必ずと言って良いほど、ゲート抵抗が挿入されています。なぜでしょうか?

以下、解説していきます。

FETゲート駆動の仕組み

まずは、Nch-FETを例に、FETゲート駆動の仕組みを説明します。

例えば、Nch-FETをONするにはソースに対するゲートの電圧(VGS)を上げる必要があります。

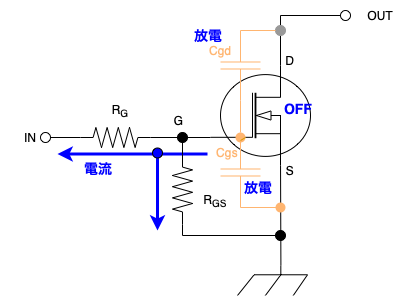

ここで、FETには入力容量(ゲート・ソース間容量:Cgs、ゲート・ドレイン間容量:Cgd)と呼ばれる容量成分があるため、

VGSを上げる = 入力容量に電荷を充電する

といえます。

逆に、Nch-FETをOFFする時は、

VGSを下げる = 入力容量から電荷を放電する

となります。

ゲート抵抗の役割

もしゲート抵抗がなければ、ゲートに印加された電源と入力容量の間が短絡に近い状態となってしまい、FETをON/OFFする(入力容量に充放電する)たび、非常に大きな電流を流さなくてはなりません。

ゲートを駆動する回路がこの電流を許容できない場合、ゲート電圧レベルを正しくドライブできなかったり、最悪の場合、ゲートドライバが破損する可能性があります。

よって、、ゲートの入力容量への充放電電流を制限するためゲート抵抗が必要になります。

Pch-FETの場合は、ONの時に放電、OFFの時に充電と逆の動作になりますが、同じことが言えます。

ゲート抵抗の決め方

上記したとおり、FETのゲートには何Ωかの抵抗を挿入する必要があります。

何Ωを挿入すれば良いでしょうか?

ゲート抵抗の下限値

まず、FETのゲートを駆動する回路(ゲートドライバ)がどれくらいの電流を流すことができるか確認します。

例として、5V入力タイプの小信号用Nch-FETのゲートを、出力電流±10mA(max)のゲートIC(CMOS出力)で駆動する場合を考えます。

このとき、

ゲート抵抗 > 5V/10mA = 500Ω

を満たす必要があります。(オームの法則)

※RGSにも電流が流れますが、説明では無視しています。後述しますが、ゲート・ソース間電圧を稼ぐためにRGSはRGよりも大きな定数となります。RGSを含めて厳密に計算するとゲート抵抗はもう少し小さくできますがあまり意味は無いと思われます。

では、500Ω以上であれば何Ωでも良いのでしょうか?

結論から言うと、電力損失(熱)の観点において、FETのゲート抵抗は可能な限り小さいほうが望ましいと言えます。

ゲート抵抗の上限値

ゲート抵抗とスイッチング損失の関係

ゲート抵抗を大きくすると入力容量への充放電電流が減り、時定数(τ=CR)が大きくなります。

つまり、

入力容量への充放電時間 = FETのON/OFF遷移時間(スイッチング時間)

が長くなります。

FETは、スイッチング損失(ON→OFFまたは、OFF→ONへ”遷移する間”の電力損失)が定常時(完全にONした後)の損失と比較して桁違いに大きいため、スイッチング時間を可能な限り短く設計することが基本となります。

ON/OFF 1周期あたりの損失を小さくすることで、チャネル温度の上昇を抑制できます。この考え方は、単位時間あたりのスイッチング頻度が多い(スイッチング周期が短い)回路ほど重要になります。

では、ゲートのスイッチング時間はどこまで長くしてよいか(ゲート抵抗の上限値は)?という話は、FETの仕様:<オン抵抗、熱抵抗、許容損失、チャネル温度定格、他>によりますので一概に言えません。

ですが、スイッチング損失に伴うチャネル温度上昇の観点から考えると、ゲート抵抗は可能な限り小さい方が望ましいということです。

ただ、スイッチング時間が早すぎると、チャネル温度の上昇を抑えることができる反面、放射ノイズの悪化、負荷側への突入電流ピークが増加する、というマイナス要因もあり、注意が必要です。

ゲート抵抗をあえて大きくするケース

逆に、スイッチング頻度が極めて低く、FETオン時に負荷容量への大きなチャージ電流が問題となるロードスイッチの用途では、あえてターン・オン時間が長くなるように設計し、負荷容量への突入電流のピークを抑えることを目的とする場合があります。

ゲート・ソース間抵抗

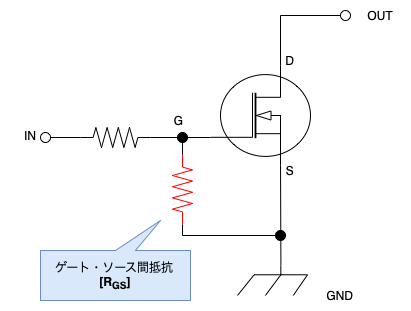

FETのゲート・ソース間に挿入する抵抗を”ゲート・ソース間抵抗”と言います。

ゲート・ソース間抵抗が必要な理由

FETのゲートがフローティングして回路が誤動作してしまうことを避けるため、ゲート-ソース間に抵抗を入れて論理固定する必要があります。

Nch、Pchどちらであっても、ゲート・ソース間に抵抗を入れるとFETがOFFする方向にゲートレベルが固定されます。

考え方は、プルアップ・プルダウン抵抗の考え方と同様です。

ゲート・ソース間抵抗の決め方

ゲート・ソース間抵抗の下限値

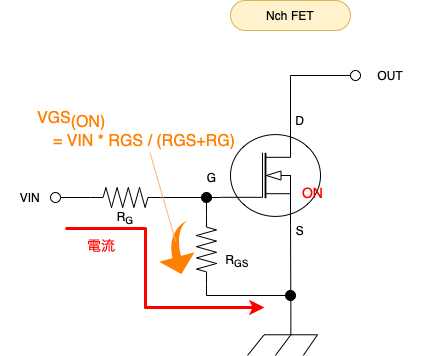

ゲート-ソース間に抵抗を挿入すると、ゲート・ソース間電圧(VGS)はゲート抵抗とゲート・ソース間抵抗で分圧されてしまいますが、それでもFETのオン閾値を超えるよう設計する必要があります。

例えば、5V入力タイプの小信号用Nch-FET(ON閾値は4Vとします)をゲート抵抗50Ωで駆動させる場合、

Vgs = ON閾値 4V < 5V * Rgs/(50Ω+Rgs)

Rgs > 262.5Ω

を満たす必要があります。

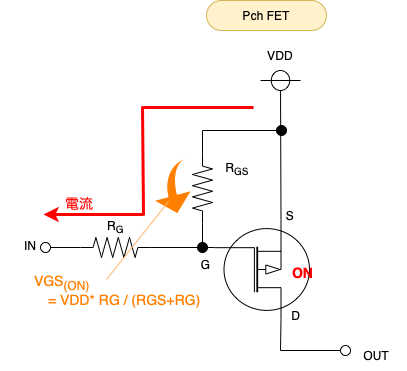

Pch-FETの場合は計算式が異なりますが、同様の考え方で計算できます(下図)

ゲート・ソース間抵抗の上限値

ゲート・ソース間抵抗の定数は大きい方がVGSを稼げるため、上限値はありません。

ですが、あまり大きすぎると、FETへのゲートソース間リーク電流(IGSS)の影響を受けるため、大きくても数十kΩ〜数百kΩ程度が良いと思います。

まとめ

ゲート抵抗

✔️ゲート抵抗は可能な限り小さくしスイッチング損失を抑えることがFET設計の基本である

✔️ただし、ゲート抵抗を小さくしすぎると以下のリスクがある

・ゲートドライバの駆動能力に対する要求が厳しくなる

・EMI性能が悪化する

・オン時に突入電流のピークが大きくなる

ゲート・ソース間抵抗

✔️ゲート・ソース間抵抗の目的はFETがOFFする方向にゲートを論理固定すること

✔️ゲート・ソース間抵抗は、十分なゲート・ソース間電圧を確保できる定数を選定する

✔️ゲートソース間抵抗を大きくしすぎるとゲート・ソース間電圧がゲートのリーク電流の影響を受ける

コメント