シングルエンド信号を差動信号に変換して出力するLVDSドライバまたは、その逆を行うLVDSレシーバの重要な特性である遅延時間とスキューについて解説します。

本記事はLVDSについての基礎知識が前提となっています。LVDSの基礎については以下の記事にまとめてありますので、合わせてお読みいただけると理解しやすくなります!

✔️LVDSドライバ/レシーバとは何か

✔️LVDSドライバ/レシーバICを用いた設計のポイント(遅延時間とスキュー)

✔️LVDS IC データシートの読み方(tpHL/tpLH、tsk(p)/tsk(o)/tsk(lim)またはtsk1〜4)

LVDSドライバ/レシーバにおけるスキューと遅延時間の考え方

LVDSドライバ/レシーバとはなにか?

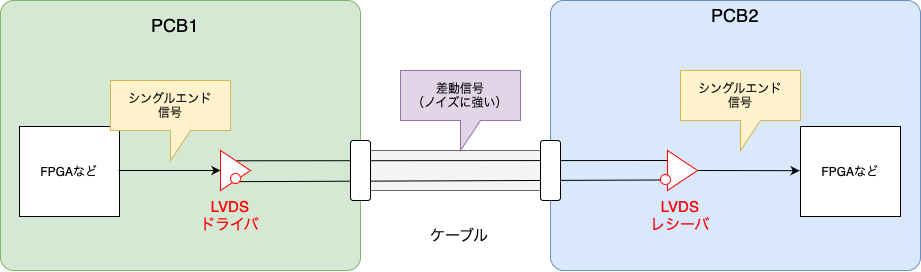

CMOSやTTLなどのシングルエンド信号を差動信号であるLVDSに変換して出力するデバイスをLVDSドライバ、逆にLVDS信号をシングルエンド信号に変換するデバイスをLVDSレシーバといいます。

私の経験上、ケーブルを用いた基板間通信を行う際ノイズに強い差動信号に変換する目的で使用されることが多い印象です。

LVDSドライバ/レシーバは様々なメーカに専用のICがラインナップされている他、LVDS出力/入力を持つFPGAのハードウエア(IO)を指すこともあります。

本記事では、基本を理解するため、主に専用ICを例に解説します(FPGAの場合も内部回路に同じことが言えます)。

遅延時間とスキュー

LVDSドライバ/レシーバICを使用した回路設計に重要となるパラメータとして、遅延時間とスキューがあります。

遅延時間とスキューの定義

遅延時間とスキューは似ているようで異なる概念です。

差動信号における遅延時間とスキューは下記で定義されます。

✔️【スキュー(skew)】異なる入出力間での遅延時間「差」

遅延時間とスキューの違い

遅延時間とスキューの違いは分かりにくいため、もう少し説明します。

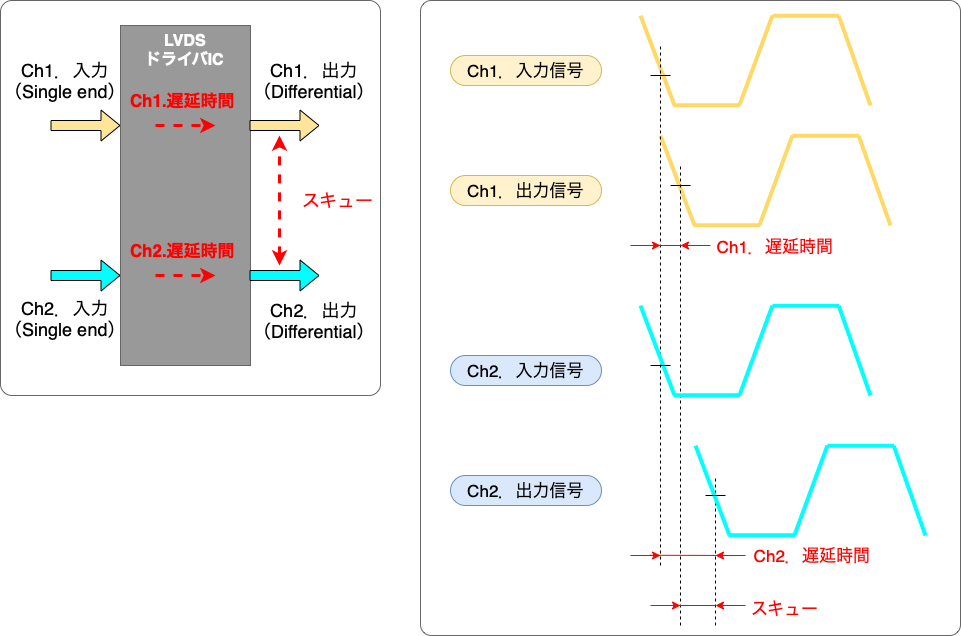

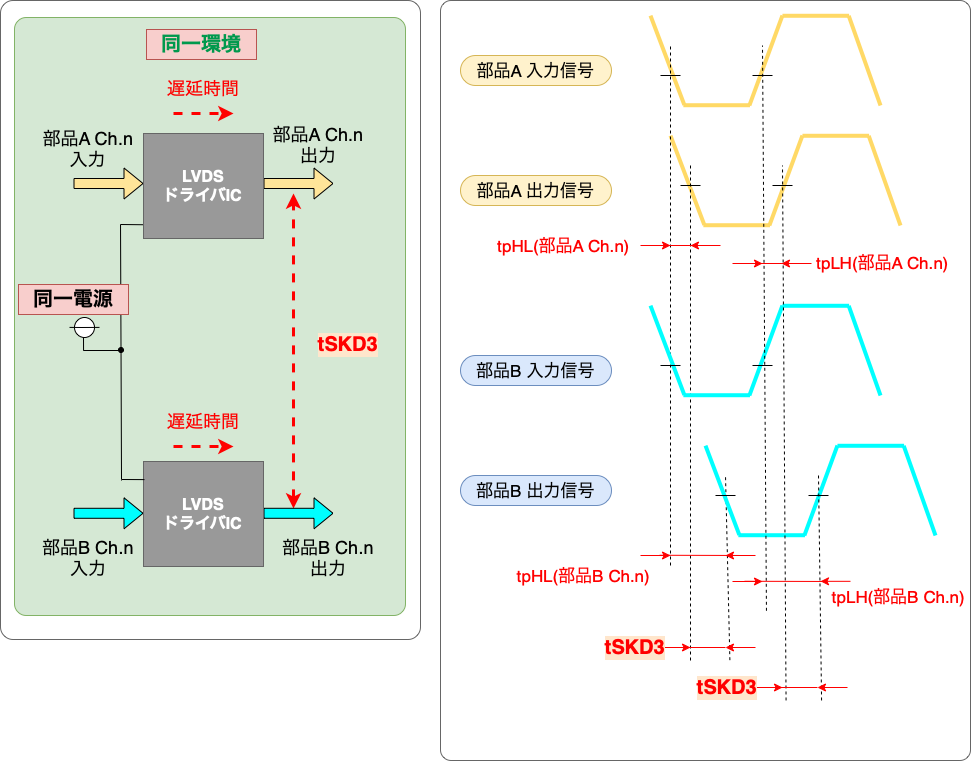

図は2チャンネルの入出力を持つLVDSドライバICを示しています。

各チャンネルの入力信号と出力信号のタイミングにはそれぞれ異なる『遅延時間』が生じます。

この遅延時間「差」が『スキュー』となります。

つまり、各チャンネルへの入力信号のタイミングが全く同じだったとしても、各チャンネルの出力信号にはズレが生じ、これをスキューと呼びます。

※図の例は『チャネル間スキュー』と言う(詳細は後述)

遅延時間やスキューが大きいと困ることは?

同期用クロックとデータを一緒に伝送する場合、スキューが大きいと、タイミングマージンの減少を招きます。

例えば、クロックエッジのど真ん中でデータを取り込むよう設計しても、クロックとデータのタイミングにスキュー分のズレが生じ、狙い通りのタイミングとならないためです。

このようなタイミングを検討する際には、データシートに記載されているスキューに関するパラメータのワーストケースでタイミングマージンを算出する必要があります。

一方、遅延時間はそれほど気にする必要が無い場合が多いです。

遅延時間は通常nsオーダであり、同期されている信号が丸ごと遅延するならば、少々遅れても問題にならないためです。

(基準クロックとデータ間のタイミングズレは問題となる場合があるが、両者が等しく遅れるのであれば問題にならない場合が多いです。同期クロックとデータを別型番のデバイスで伝送していれば遅延時間の差でスキューが生じますが、そのような使い方は稀でしょう。)

上記はLVDSドライバの例ですが、LVDSレシーバの場合も全く同様のことが言えます。

LVDSドライバ/レシーバ ICの特性

LVDSドライバ/レシーバICは、様々なメーカに専用のデバイスがラインナップされています。

これらデバイスには様々な条件における遅延時間やスキューが規定されています。

LVDSドライバ/レシーバIC データシートの読み方

LVDSドライバ/レシーバICのデータシートには遅延時間やスキューに関する様々なパラメータが記載されていますが、これが非常に分かりにくいため、以下に整理して解説します。

伝搬遅延時間(Differential propagation delay :tPHLD、tPLHD)

伝搬遅延時間は、入力側での信号変化が出力側に反映されるまでの遅延時間を示します。

Differential propagation delay high to low:

入力信号のレベルがHからLに遷移するとき、その遷移が出力に伝搬するまでの遅延時間

Differential propagation delay low to high:

入力信号のレベルがLからHに遷移するとき、その遷移が出力に伝搬するまでの遅延時間

一般的に、パラメータのシンボルはそれぞれ『tPHLD』、『tPLHD』と定義されます。

このパラメータはMin〜Maxの範囲で定義されますが、これは同一チャンネル内でばらつきをもつこと意味します。

遅延時間のばらつきは、後述するデバイス間スキューを考える上で重要となります。

差動パルススキュー(Differential pulse skew:tSKD1またはtSK(p) )

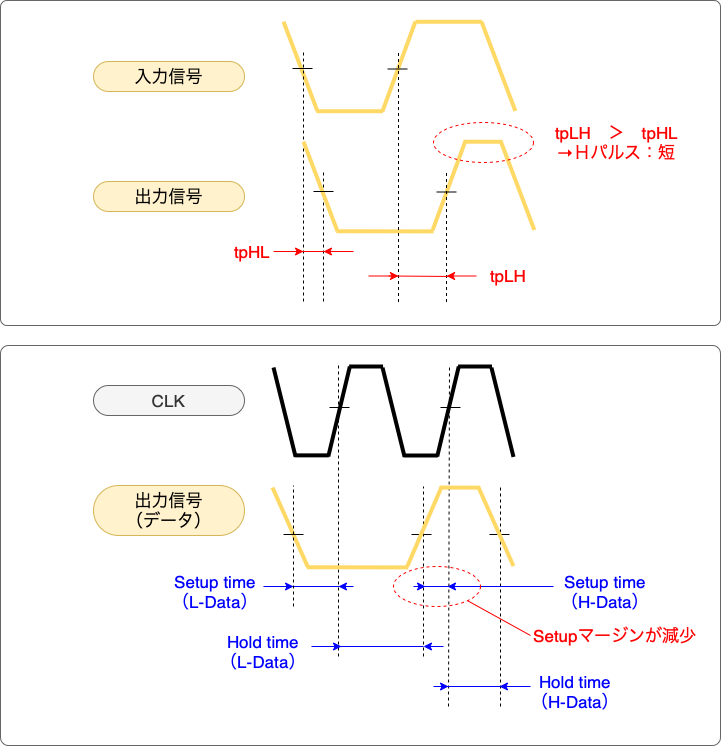

差動パルススキューは、同一チャンネルにおける、tPHLDとtPLHDの差(|tPHLD-tPLHD|)と定義されます。

これは、入力のHパルス幅とLパルス幅が同一であったとしても、出力のHパルスとLパルスの幅には差が出ることを示しています。

計算してみると分かりやすいですが、tPHLD>tPLHDの場合、出力のHパルスはLパルスよりも短く、tPLHD>tPHLDの場合、出力のLパルスはHパルスよりも短くなります。

例えば、入力が周期20ns、duty比50%のクロック信号で、データシートで規定される差動パルススキューが-400psであった場合、Hパルス幅とLパルス幅は下記となります。

Hパルス幅 = 20ns/2 + 400ps = 10.4ns

Lパルス幅 = 20ns/2 - 400ps = 9.6ns

duty比は52%

パルス幅の増減は、クロックに対するセットアップ、ホールド時間など、タイミングマージンの減少を招きます。

パラメータのシンボルはメーカによって異なりますが、『tSKD1』または『tSK(p)』と定義されることが一般的です。

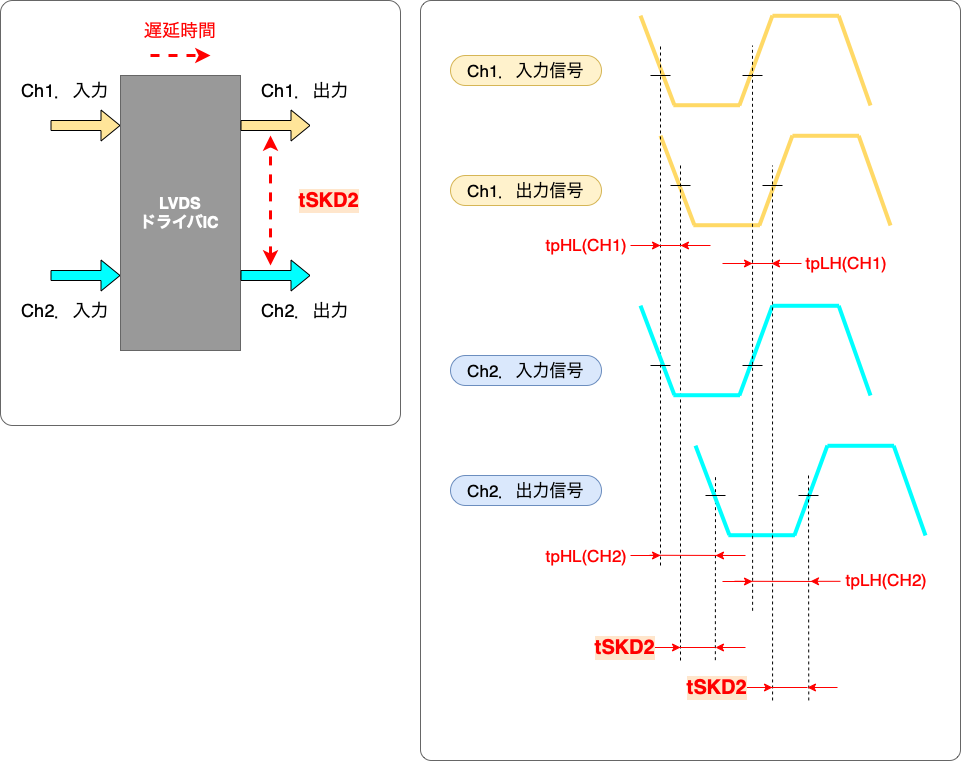

チャンネル間スキュー(Channel to channel skew:tSKD2またはtSK(o) )

チャンネル間スキューは、同一デバイス内、異なるチャンネル間のスキューです。

LVDSドライバ/レシーバICは複数の入出力チャンネルを持つものが一般的ですが、チャンネルごとに遅延時間がばらつく(出力間にスキューがある)ことを意味しています。

パラメータのシンボルはメーカによって異なりますが、『tSKD2』または『tSK(o)』と定義されることが一般的です。

部品間スキュー(Differential part to part skew:tSKD3またはtSK(pp) )

部品間スキューは、異なる部品(同一型番の別個体)間のスキューです。

同一型番の部品でも、個体ごとに遅延時間がばらつく(出力間にスキューがある)ことを意味しています。

この概念は上記チャンネル間スキューの上位にあたり、より大きなスキュー値が規定されます。

部品間スキュー > チャンネル間スキュー

パラメータのシンボルはメーカによって異なりますが、『tSKD3』または『tSK(pp)』と定義されることが一般的です。

tSKD3またはtSK(pp)は、同一電源、同一環境下にある部品間に適用されます。

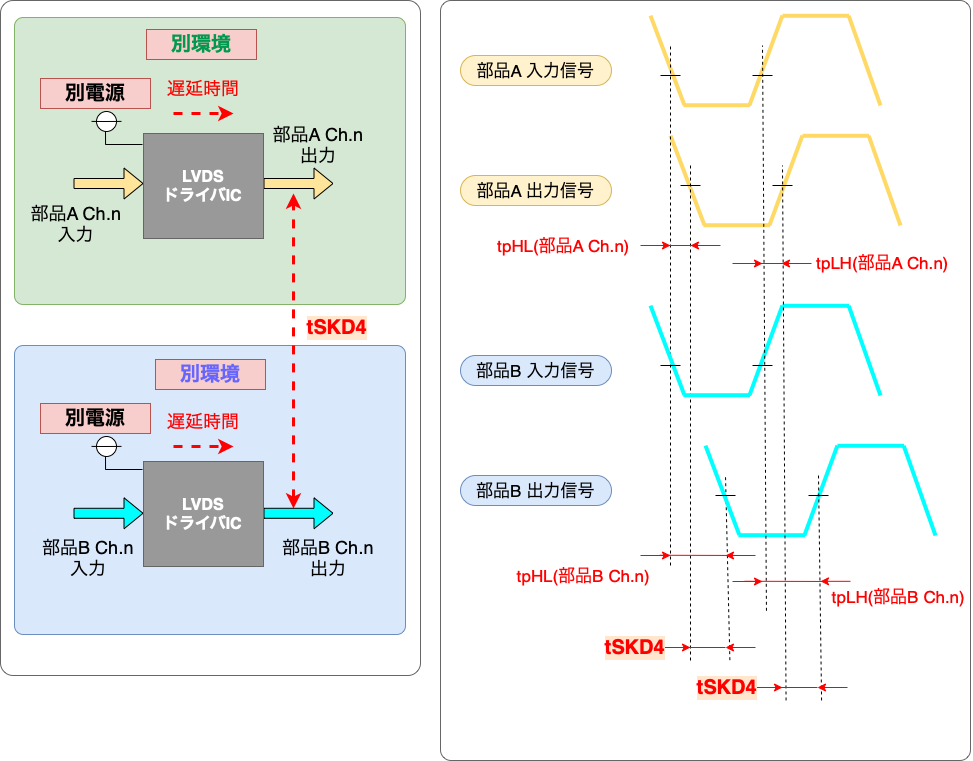

部品間スキュー(Differential part to part skew:tSKD4またはtSK(lim) )

上記同様、部品間スキューで、考え方としてはtSKD3またはtSK(pp)と同一です。

同じ”Differential part to part skew”という名称で定義されているデータシートが一般的です。

パラメータのシンボルはメーカによって異なりますが、『tSKD4』または『tSK(lim)』と定義されることが一般的です。

異なる点は、tSKD3またはtSK(pp)にある”同一電源、同一環境下にある部品間に適用”という条件が無い(デバイスの動作保証条件の全範囲に適用)ことです。

つまり、同一型番である限り、個体ばらつきや使用条件を含め、全出力間で最大のスキュー値をとります。

前述したように、スキューというのはチャンネルごとの遅延時間差ですから、tSKD4またはtSK(lim)は、tPHLD、tPLHD差のワースト(max-min)に等しくなります。

tSKD4またはtSK(lim) = tPHLD(max) - tPHLD(min) または、

tPLHD(max) - tPLHD(min)

その他(LVDS SerDes)

上記した単純なLVDSドライバ/レシーバIC以外に、LVDS SerDesと呼ばれる専用部品が存在します。

SerDesとは、Seriarizer/Deseriarizerの略称で、CMOS等のパラレル信号をLVDS信号にシリアライズしたり、逆にLVDS信号をデシリアライズするための回路です。

SerDesには別途様々な仕様値が規定されていますが、こちらについては下記ページにて詳しく説明しています!

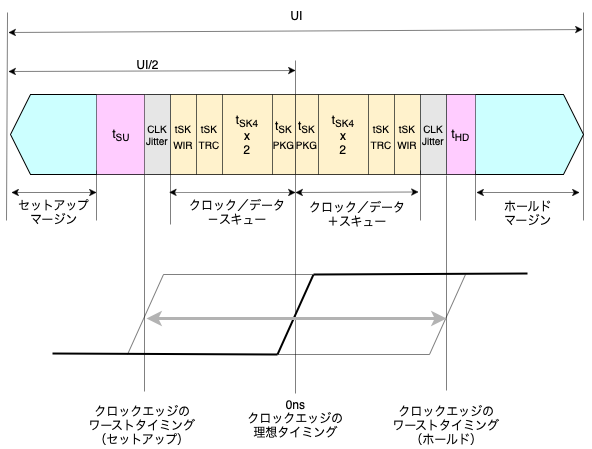

スキューを考慮したLVDS伝送路の設計

LVDS伝送線路を設計する際には、タイミングマージンの検証が必須です。

タイミングマージンは、ユニットインターバル(データ1bit分の幅:以下『UI』)から、伝送線路内のスキュー、クロックのジッタ、受信デバイスのタイミング要求を差し引いて求めます。

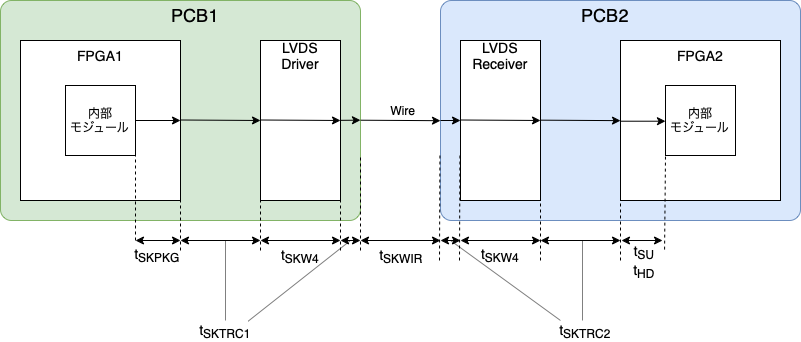

LVDS伝送路の設計例

例として、下図のように基板[1](FPGA→LVDSドライバ)から、基板[2](LVDSレシーバ→FPGA)へLVDS信号を伝送する例を想定します。

同期クロックは20MHz、データとは別のLVDSチャンネルとします。

以下に記載する具体的数値は一例です。実際に使用するデバイスのデータシートを確認します。

UI = 1/20MHz = 50ns

スキュー(tSKW) = 下記❶〜❻の合計 = ±4.18ns

❶FPGA[1]のパッケージスキュー tSKPKG = ±100ps(FPGA[1]データシートより)

❷LVDSドライバの部品間スキュー tSKW4 = ±2ns(ドライバICデータシートより)

❸基板[1]のトレース間スキュー tSKTRC1 = ±20ps(PCB配線長差、材料より算出)

❹基板[1]-[2]間ワイヤ長差スキュー tSKWIR = ±50ps(線材長差、材料より算出)

❺基板[2]のトレース間スキュー tSKTRC2 = ±10ps(PCB配線長差、材料より算出)

❻LVDSレシーバの部品間スキュー tSKW4 = ±2ns(レシーバICデータシートより)

クロックのジッタ(CLKj) = ±200ps(FPGA[1] ツールで内蔵PLL出力の精度を算出)

FPGA[2]タイミング要求(tsu、thd)

クロックに対するデータセットアップ時間 = 3ns(FPGA[2]データシートより)

クロックに対するデータホールド時間 = 1ns(同上)

以上より、

セットアップマージン

= UI/2 ー(tSKW + tsu + CLKj) = 25ns ー(4.18ns + 3ns +0.2ns)= 17.62ns

ホールドマージン

= UI/2 ー(tSKW + thd + CLKj) = 25ns ー(4.28ns + 1ns +0.2ns)= 19.62ns

となります。

コメント