電気回路の解説を読むと、「入力インピーダンスが高いため...」や、「出力インピーダンスが低いため...」といった表現をよく見かけます。

でも、新人のエンジニアには、これがなにを意味するのか、分かるようでいまいち分からない、という方も多いのではないでしょうか。

よく、入力インピーダンスは「回路を入力側からみたときのインピーダンスである」とか、出力インピーダンスは「回路を出力側からみたときのインピーダンスである」と説明されます。

私は最初、この概念を大学の講義で学びましたが、正直そのときは難しい式もたくさん出てきてなにを言っているのか全く分からなかったものです。

本記事では、これら入力インピーダンスと出力インピーダンスについて、分かりやすく、実用レベルに落とし込んで説明していきます!

✔️入力インピーダンス、出力インピーダンスの概念

✔️入力インピーダンスは高い方が良い理由

✔️出力インピーダンスは低い方が良い理由

※本記事の内容は電気回路初心者向けです

そもそもインピーダンスとはなにか

入力インピーダンス、出力インピーダンスについて語る前に、そもそもインピーダンスとはなにか、をざっくり説明します。

インピーダンスとは、「交流会路における電流の流れやすさ」を意味します。

これはwebで検索すればすぐに出てきますが、要するに直流回路でいう「抵抗(R)」のことです。

交流の場合は抵抗の他、電圧・電流の時間変化によって「電流の流れにくさ」が変化するリアクタンス(容量CやインダクタンスL)があるため、これらを合成した流れにくさをインピーダンスと呼びます。

本記事の目的は入力インピーダンスと出力インピーダンスの概念を説明することなので、話を簡単にするため、以下直流回路(インピーダンス=直流抵抗R)であることを前提に進めます。

すなわち、本記事内では「入力インピーダンス」は「入力抵抗」と、「出力インピーダンス」は「出力抵抗」と、読み替えても構わないということになります。

入力インピーダンス・出力インピーダンスの概念

本題です。

まずは、入力インピーダンスと出力インピーダンスの概念(考え方)を説明します。

で、これってなにに使うの?は後ほど説明します。

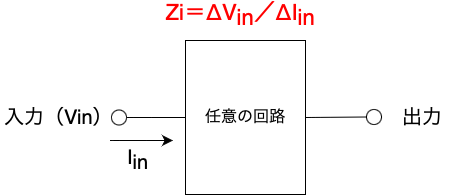

入力インピーダンスとは

入力インピーダンス(Zi)とは、「ある回路の入力電圧変化(ΔVin)を、入力端子に流れ込む電流変化(ΔIin)で割ったもの」と定義できます。

Zi = ΔVin/ΔIin

後の出力インピーダンスの説明と合わせるために少し回りくどい言い方になりましたが、要するにただオームの法則で入力抵抗を導いいただけです。

これは、「入力抵抗」のイメージそのままだと思います。

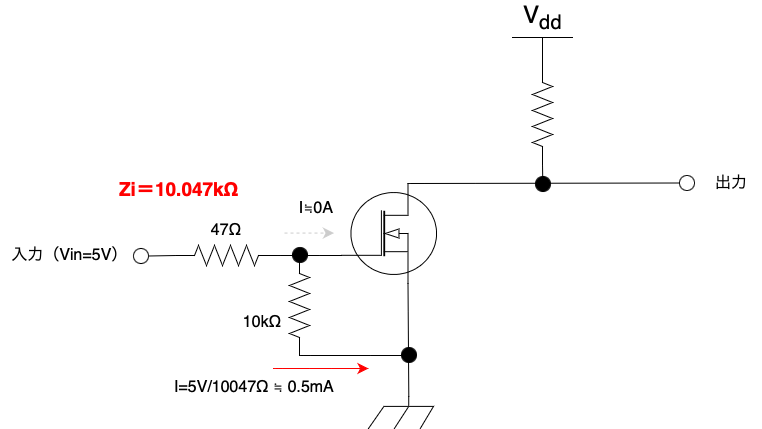

仮に入力端子に5Vを印加し、約0.5mAの電流が流れたとすると、Zi=5V/0.5mA=10kΩと分かります。

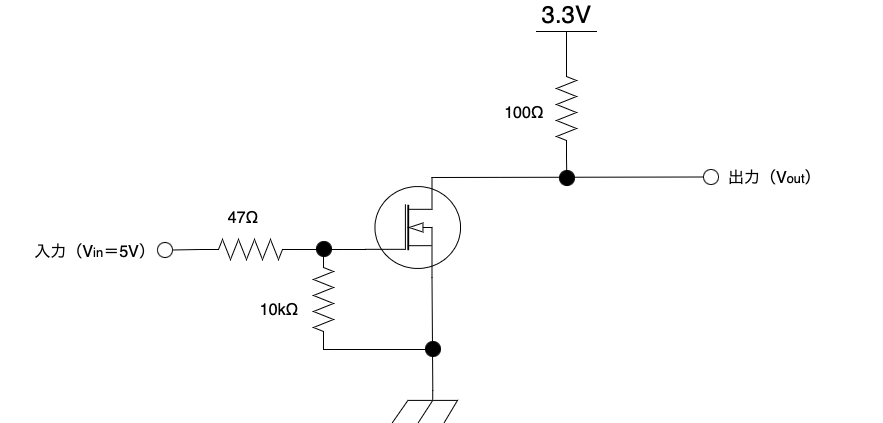

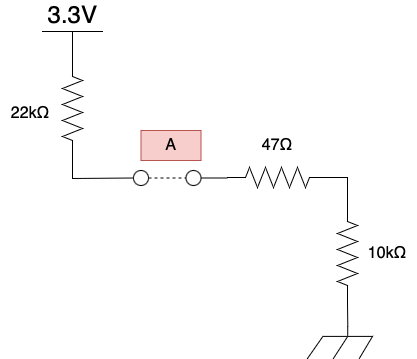

以下、Nch MOS FETを用いたインバータ回路を例に説明します。

この回路は入力電圧が5V、ゲート抵抗が47Ω、プルダウン抵抗が10kΩであるものとします。なお、FETのゲートに流れ込む電流は微小なので無視します。

この回路は、Zi = 47Ω+10kΩ = 10.047kΩとなります。

ちなみに、入力端子に流れ込む電流は5V/(10.047kΩ) ≒ 0.5mAとなります。

直流回路(Z=R)なのでそのままですね。

FETのゲートに流れ込む電流は微小なので無視すると書きました。

FETはゲートの直列抵抗が非常に大きく、直流を印加している限り、電流がほとんど流れないためです。

これは、「FETは入力インピーダンスが非常に高い」と表現できます。

上図回路全体でみたとき入力インピーダンスは10.047kオームでしたが、FETをひとつの回路としてみたとき、入力インピーダンスはもっと大きくなります(数MΩ以上)。

このように、入力・出力インピーダンスの値は回路をどこで区切るかによって異なります。

というより、入力・出力インピーダンスはあくまで「任意区間の回路」に対する概念であることに注意してください。例えば、電源からGNDまでとか、ICの入力から出力まで、とかいった決まりはありません。

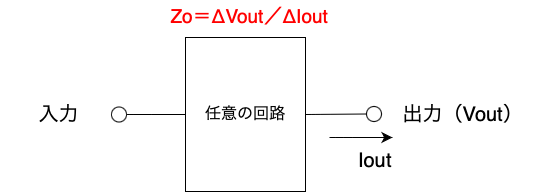

出力インピーダンスとは

出力インピーダンス(Zo)とは、「ある回路における出力の負荷変動(ΔIout)で、それによる出力端子の電圧降下(ΔVout)で割ったもの」と定義できます。

Zo = ΔVout/ΔIout

負荷を大きくしていくと、出力インピーダンスによる電圧効果で力電圧が降下していきます。

仮に、出力端子に1mAの負荷を接続し、出力電圧が0.1V低下したとすると、Zo=0.1V/1mA=100Ωであると分かります。

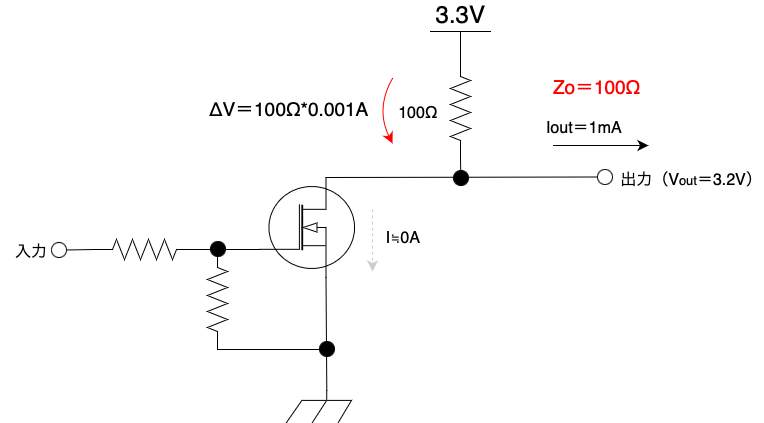

具体的に、Nch MOS FETを用いたインバータ回路を例に説明します。

この回路の出力電圧を3.3V、プルアップ抵抗を100Ω、負荷を1mAとします。

出力端子から電流を流す想定ですので、FETはオフしているものとします。なお、FETオフ時、ドレイン・ソース間に流れる電流は微小であるため無視します。

このとき、Zo=100Ωです。

ちなみに出力電圧は、3.3V – 100Ω*1mA = 3.3V – 0.1V = 3.2Vとなります。

直流回路(Z=R)なのでそのままですね。

入力・出力インピーダンスを考慮した設計

ここまでは、入力・出力インピーダンスの概念を説明しました。

この概念を回路設計にどう活かすのか?について以下説明していきます!

入力インピーダンス>>出力インピーダンスの関係

まず、回路設計の基本として、2つの回路を接続するとき、後段回路の入力インピーダンスは前段回路の出力インピーダンスよりも十分に大きくする必要があります。

入力インピーダンス >> 出力インピーダンス

これをよく「ハイ受けロー出し」なんて言ったりしますが、そのくらい基本となる概念です。

なぜこれが基本なのでしょうか。以下に説明していきます!

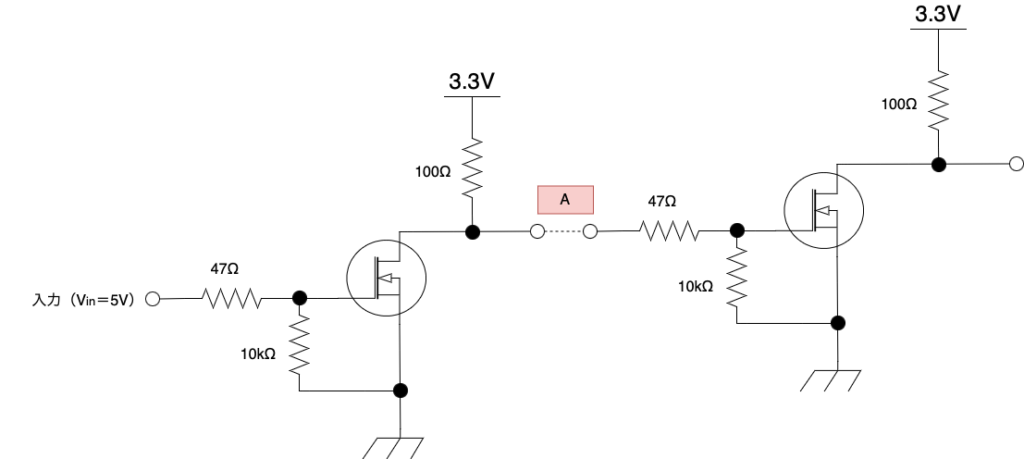

再び下図の回路で考えます。

上述したように、この回路は、入力インピーダンス10.047kΩ、出力インピーダンス100Ωです。

この回路を二つ接続してみます。

(入力インピーダンスは出力インピーダンスの約100倍なので、まあ、Zi>>Zoと言えるかな。)

さて、前段回路のFETがオフのとき、出力(「A」で示したポイント)の電圧はいくらになるでしょうか。

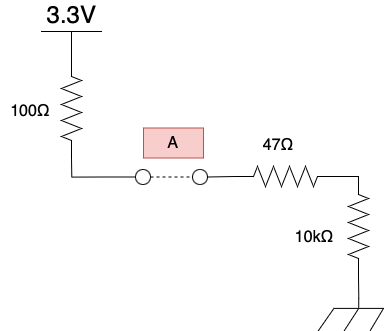

前段回路のFETのドレインおよび、後段回路のFETのゲートに流れる電流は微小ですので、等価回路は下図となります。

このとき、Aポイントの電圧=3.3V*(10k+47)/(100+10k+47)=3.27Vとなります。

前段回路の出力電圧は多少(0.03V)降下しましたが、この程度であればきちんとハイレベルを伝達できるといえでしょう。

では、もし逆に入力インピーダンス<出力インピーダンスだとどうなるでしょうか。

例えば、同様の回路で前段回路のプルアップ抵抗(出力インピーダンス)を22kΩとします。

この場合、VA=3.3V*(10k+47)/(22k+10k+47)=1.03Vとなり、本来は3.3Vを伝達すべきハイレベル信号が半分以下になってしまいました。

このように、入力インピーダンス>>出力インピーダンスでないと、前段回路の出力インピーダンスにより出力電圧がドロップしてしまい、電圧レベルを正しく出力できません。

入力インピーダンスと出力インピーダンスは、その「差」が大きいほど出力電圧のドロップを抑えられます。

AC/DC、DC/DC等、電源モジュールも出力インピーダンスをもった回路です。

ただ、これらは電力供給が目的ですので、出力インピーダンスが極めて小さくなるように設計されています(数mΩとかいうレベルです)。

このため、ちゃんとした負荷(ある程度の抵抗値をもった負荷)を接続している限り、これによる出力電圧のドロップを気にする必要はほとんどありません。

電源モジュールの出力に数Ω〜数mΩの負荷を接続すると電源モジュールの出力電圧もさすがにドロップしますが、こうなるともうほぼ短絡状態(アブノーマル状態)といえます。

電流定格も超えるでしょうし、実使用の範囲ではありえないでしょう。

入力・出力インピーダンスの大きさ

入力インピーダンス>>出力インピーダンスは基本であるものとして、この関係を守ったうえで、

入力・出力インピーダンスは大きい方が良いのか?小さい方が良いのか?

ここはメリット・デメリットがそれぞれあるので、状況に応じて設計が必要となります。

入力・出力インピーダンスが高い

入力・出力インピーダンスが全体的に高いということは、省電力である反面、電力の伝達はできないことを意味します。

入力・出力インピーダンスが高い:メリット

たとえば、下図左(入力・出力インピーダンスが高い)と下図右(入力・出力インピーダンスが低い)はどちらも入力インピーダンス・出力インピーダンス比が100:1の関係(上記入力インピーダンス>>出力インピーダンスの関係)なので、伝達する電圧レベルは同じになります(3.27V)。

でも、流れる電流を計算すると下図左の方が遥かに省電力です(下図左に流れる電流は3.37uA、下図右に流れる電流は327mA)。

また、上図左は低損失な分、部品のパッケージサイズを小さくでき高集積化しやすいという特徴があります。

以上より、入力・出力インピーダンスが高い回路は、高集積、省電力が要求されやすく、電圧レベルだけを伝達すれば良いデジタル回路向き、といえます。

上図は簡易的に抵抗器のみによる回路を示しました。

実際にはこのような回路は無いので、少し分かりにくかったかもしれません。

実際の入力・出力インピーダンスが高いデジタル回路の例として、半導体ICがあります。

半導体IC(ロジックIC、マイコン)は入力インピーダンス数MΩ、出力インピーダンスは数10Ω程度です。

実際のインピーダンス値はモノによりますが、もし気になるのであれば以下の方法で把握できます(設計上あまり気にする必要はありません)。

半導体ICには入力リーク電流という特性がデータシートに記載されており、これは通常1uAとかです。

入力電圧が5Vのときの入力リーク電流が1uAであれば、入力インピーダンスは5V/1uA = 5MΩと導けますね。

一方、出力インピーダンスはデータシートからは読み取りづらいですが、最大出力電流IOHを負荷としたとき、出力電圧が出力電圧範囲VOH(min)に収まると考えれば、なんとなく導けます。

Vcc=5V、出力電流(max)=12mAのとき、出力電圧範囲VOH(min)=4Vが保証されている場合、出力インピーダンスは(5V-4V)/12mA=83.3Ω以下となるはずです。

入力・出力インピーダンスが高い:デメリット

入力・出力インピーダンスが高いと、負荷に大きな電流を流すことができません。

というより、インピーダンスが高い回路に大きな電流を流すためには、大きな電圧が必要となり、消費電力、熱損失も大変なことになるため、実用的ではありません。

つまり、入力・出力インピーダンスが高い回路は、電力を伝達する用途(モータ駆動など)に使用できません。

また、回路のインピーダンスが高すぎるとノイズ耐性が低下します(同じ電流変化でも電圧値に与える影響が大きいため)。

このような場合は、入力にプルダウン抵抗を挿入してインピーダンスを下げる方法が有効です。

電力供給を目的とした負荷、たとえばDCモータは上記の理由により、入力インピーダンスが数Ω程度となるよう設計されています。

これを入力インピーダンス>>出力インピーダンスの原則に照らし合わせると、出力インピーダンスが更に小さなドライバが必要になります。

ロジックICの出力ピンにDCモータを接続してもモータを回せないですよね。

DCモータを回すには、オン抵抗が数十mΩのFETなどが必要になることが分かると思います。

入力・出力インピーダンスが低い

入力・出力インピーダンスが全体的に低いということは高効率で電力の伝達が可能となる反面、消費電力が大きくなることを意味します。

入力・出力インピーダンスが低い:メリット

上記、入力・出力インピーダンスが高い場合のデメリットで説明した理由により、電力の伝達効率が良くなります。

入力・出力インピーダンスが低い:デメリット

上記、入力・出力インピーダンスが高い場合のメリットで説明した理由により、消費電力が大きくなります。

また、熱損失を抑えるためパッケージサイズが大きな部品を選定する必要があり、高集積化に不向きです。

まとめ

長くなってしまいましたが、入力・出力インピーダンスの概念を知らなかったとしても、内容は普段の設計で考慮していることばかりだと思われませんでしたか。

- 回路と回路を接続したときに信号がきちんと伝わるか(電圧レベルが分圧されて損なわれないか)

- 負荷に必要な電力を供給できるか

- 消費電力はシステム要件を満たすか

など。

本記事で最も重要なのが、

入力インピーダンス>>出力インピーダンス

の関係です。

これを守ったうえで、入力・出力インピーダンスの高低によってもメリット、デメリットがありますが、上述したようにこれは普通に設計していれば自然と意識する内容なので、あまり気にしなくても良いかもしれません。

- 入力・出力インピーダンスが高いと、少ない消費電力でデジタル信号(電圧レベル)を伝達できるが、電力の伝達には向かない

- 入力・出力インピーダンスが低いと、効率良く電力を伝達できるが、消費電力は大きくなる

コメント